A level-to-pulse converter produces a single cycle pulse each time its input goes high. It’s a synchronous rising-edge detector. Sample uses:– Buttons and switches pressed by humans for arbitrary periods of time – Single-cycle enable signals for counters.

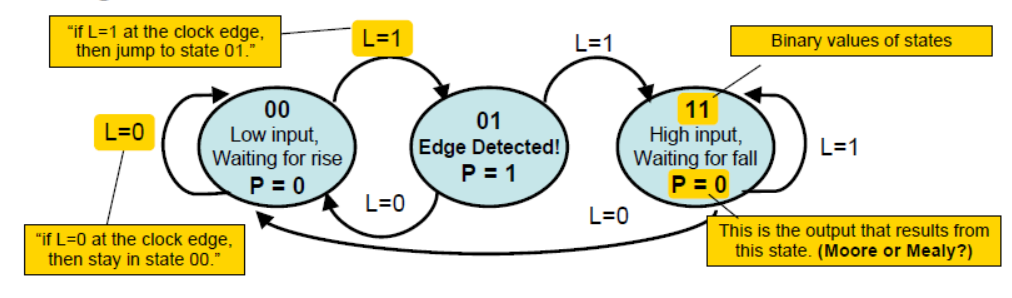

Type[1] >> This is the moore fsm for the level to pulse design.State transition diagram is a useful FSM representation and Transition diagram is readily converted to a state transition table (just a truth table).

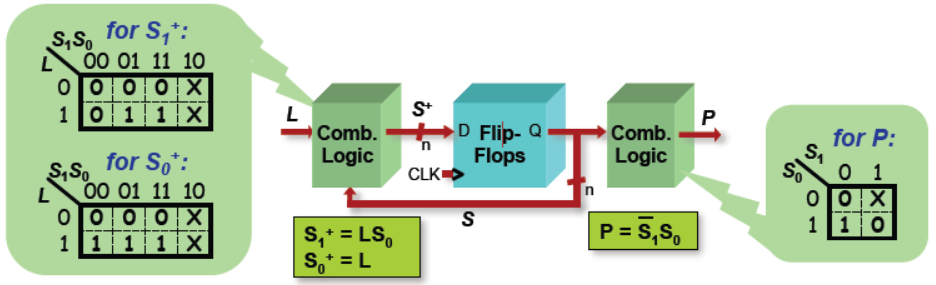

Combinational logic may be derived using Karnaugh maps

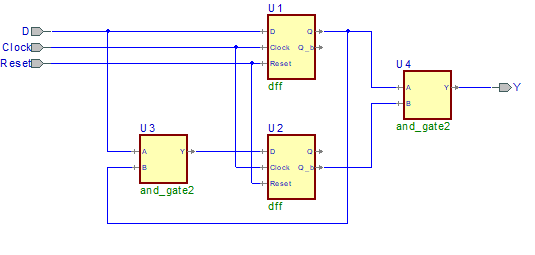

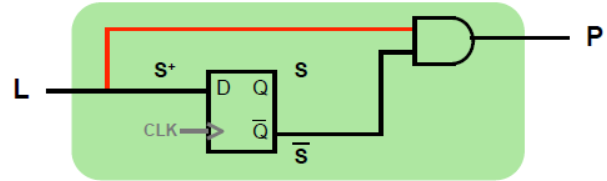

Moore FSM circuit implementation of level-to-pulse converter:

code is given below for moore fsm

library IEEE;

use IEEE.std_logic_1164.all;

entity moore_LTP_fsm1 is

port (

clk: in STD_LOGIC;

L: in STD_LOGIC;

rst: in STD_LOGIC;

P: out STD_LOGIC);

end moore_LTP_fsm1;

architecture moore_LTP_fsm1_arch of moore_LTP_fsm1 is

-- SYMBOLIC ENCODED state machine: Sreg0

type Sreg0_type is (

S1, S2, S3

);

-- attribute enum_encoding of Sreg0_type: type is ... -- enum_encoding attribute is not supported for symbolic encoding

signal Sreg0, NextState_Sreg0: Sreg0_type;

-- Declarations of pre-registered internal signals

signal int_P, next_P: STD_LOGIC;

begin

-- concurrent signals assignments

-- Diagram ACTION

----------------------------------------------------------------------

-- Machine: Sreg0

----------------------------------------------------------------------

------------------------------------

-- Next State Logic (combinatorial)

------------------------------------

Sreg0_NextState: process (int_P, L, Sreg0)

begin

NextState_Sreg0 <= Sreg0;

-- Set default values for outputs and signals

next_P <= int_P;

case Sreg0 is

when S1 =>

next_P <= '0';

if L='1' then

NextState_Sreg0 <= S2;

elsif L='0' then

NextState_Sreg0 <= S1;

end if;

when S2 =>

next_P <= '1';

if L='0' then

NextState_Sreg0 <= S1;

elsif L='1' then

NextState_Sreg0 <= S3;

end if;

when S3 =>

next_P <= '0';

if L='0' then

NextState_Sreg0 <= S1;

elsif L='1' then

NextState_Sreg0 <= S3;

end if;

--vhdl_cover_off

when others =>

null;

--vhdl_cover_on

end case;

end process;

------------------------------------

-- Current State Logic (sequential)

------------------------------------

Sreg0_CurrentState: process (clk)

begin

if clk'event and clk = '1' then

if rst='1' then

Sreg0 <= S1;

else

Sreg0 <= NextState_Sreg0;

end if;

end if;

end process;

------------------------------------

-- Registered Outputs Logic

------------------------------------

Sreg0_RegOutput: process (clk)

begin

if clk'event and clk = '1' then

if rst='1' then

int_P <= '0';

else

int_P <= next_P;

end if;

end if;

end process;

-- Copy temporary signals to target output ports

P <= int_P;

end moore_LTP_fsm1_arch;

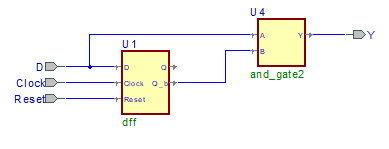

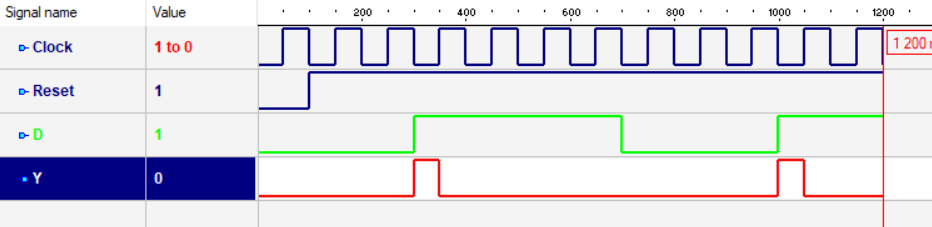

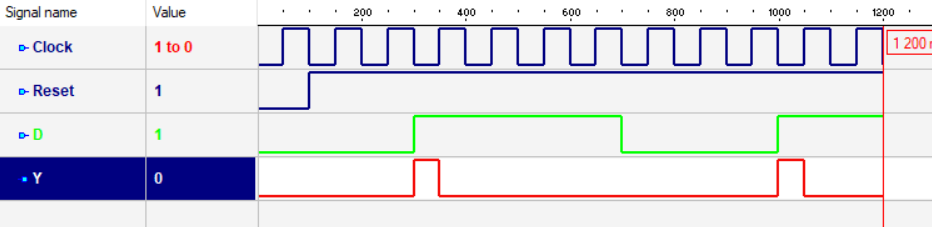

Moore circuit with its waveform.

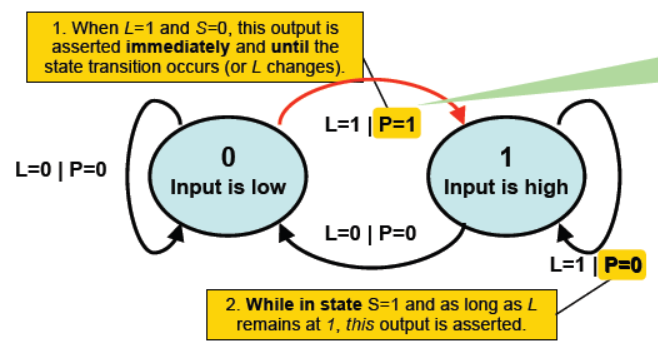

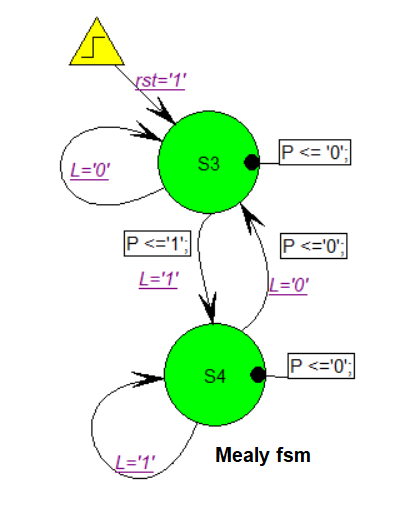

Type [2]>>Design of a Mealy Level-to-Pulse. Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations.

Its state transition table.

FSM’s state simply remembers the previous value of L • Circuit benefits from the Mealy FSM’s implicit single cycle assertion of outputs during state transitions.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_signed.all;

entity mealy_LTP_fsm1 is

port (

clk: in STD_LOGIC;

L: in STD_LOGIC;

rst: in STD_LOGIC;

P: out STD_LOGIC);

end mealy_LTP_fsm1;

architecture mealy_LTP_fsm1_arch of mealy_LTP_fsm1 is

-- SYMBOLIC ENCODED state machine: Sreg0

type Sreg0_type is (

S3, S4

);

-- attribute enum_encoding of Sreg0_type: type is ... -- enum_encoding attribute is not supported for symbolic encoding

signal Sreg0: Sreg0_type;

begin

-- concurrent signals assignments

-- Diagram ACTION

----------------------------------------------------------------------

-- Machine: Sreg0

----------------------------------------------------------------------

Sreg0_machine: process (clk)

begin

if clk'event and clk = '1' then

if rst='1' then

Sreg0 <= S3;

-- Set default values for outputs, signals and variables

-- ...

P <= '0'; else -- Set default values for outputs, signals and variables -- ... case Sreg0 is when S3 =>

P <= '0';

if L='1' then

Sreg0 <= S4;

P <= '1';

elsif L='0' then

Sreg0 <= S3; end if; when S4 =>

P <= '0';

if L='1' then

Sreg0 <= S4;

elsif L='0' then

Sreg0 <= S3;

P <= '0'; end if; --vhdl_cover_off when others =>

null;

--vhdl_cover_on

end case;

end if;

end if;

end process;

end mealy_LTP_fsm1_arch;

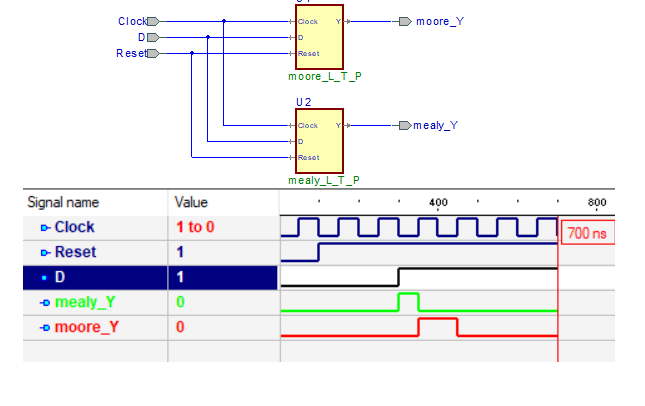

Moore/Mealy Trade-Offs • How are they different? – Moore: outputs = f( state ) only – Mealy outputs = f( state and input ) – Mealy outputs generally occur one cycle earlier than a Moore:

• Compared to a Moore FSM, a Mealy FSM might… – Be more difficult to conceptualize and design – Have fewer states

moore fsm and its waveform based on fsm only , seen same result as that of earlier.

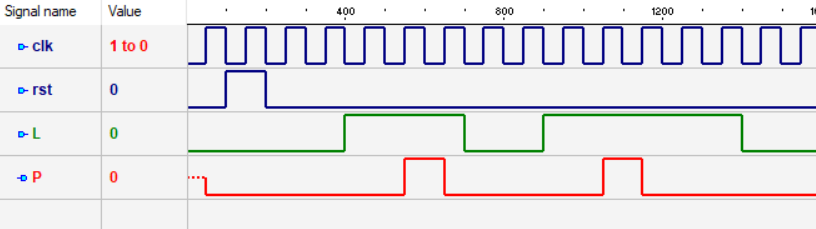

here also mealy fsm and its waveform based on fsm only , seen same result as that of earlier.

let see what will happens after rtl to gate net list transformation using synthesis tool.

Please feel free to drop comment for your quires, codes will be provided on request for free.

إن تركيبات uPVC التي ينتجها مصنع إيليت بايب Elite Pipe مقاومة للغاية للتآكل ، وتوفر حلولاً موثوقة وخالية من الصيانة لأنظمة الري والسباكة.

Thank you for the auspicious writeup. It in fact was a amusement account it.

Look advanced to far added agreeable from you! By the way, how could we communicate?

I was more than happy to discover this page.

I need to to thank you for ones time for this particularly fantastic read!!

I definitely really liked every little bit of it and i also have you book-marked to see new things in your

blog.

With havin so much content and articles do you ever run into any issues

of plagorism or copyright violation? My site has a lot of unique content I’ve either written myself or outsourced but it seems a lot of it is popping it up all over the internet without my authorization. Do you

know any ways to help stop content from being ripped off?

I’d truly appreciate it.

I blog frequently and I seriously thank you for your

content. The article has truly peaked my interest.

I am going to take a note of your website and keep checking

for new information about once per week. I opted in for your RSS

feed too.

If you wish for to improve your familiarity only keep visiting

this web page and be updated with the newest information posted here.

Great blog! Is your theme custom made or did you download it from somewhere?

A design like yours with a few simple tweeks

would really make my blog shine. Please let me know where

you got your theme. Thank you

Useful information. Lucky me I found your website by accident, and I am shocked

why this accident did not happened in advance!

I bookmarked it.

Thanks for sharing superb informations. Your web site is so cool. I’m impressed by the details that you have on this site. It reveals how nicely you perceive this subject. Bookmarked this website page, will come back for more articles. You, my friend, ROCK! I found simply the information I already searched all over the place and just could not come across. What a great web site.

yandanxvurulmus.tz0UQTs7509Y

xyandanxvurulmus.GzDxsR0Ek1Gc

xbunedirloooo.dlZ429ecUdaZ

porn siteleri vurgunyedim.u96meOayp9r3

childrens sex yaralandinmieycan.xvGmOvQD5gqc

porn citixx.c9acLDMbjyFk

bahis siteleri porn sex incest hyuqgzhqt.TfKQtv6qOUs0

watch porn video ewrjghsdfaa.ye7YH2mDWcVk

house porn wrtgdfgdfgdqq.p5HOVCA8W4fN

porno siteleri wrtgdfgdfgdqq.fJcIAIFDVkPR

amciik siteleri hepxhupx.pxT9ETtasUa0

bahis siteleri porn sex incest juljulfbi.F8jPc5J5pgsZ

bahis siteleri incest category bjluajszz.StoHKkz8f02Z

porn siteleri bxjluajsxzz.p45LNI71N3lQ

bahis siteleri sikis 0qbxjluaxcxjsxzz.OuJmaS4TtVP6

house porn pokkerx.xHHDLqK4bMwQ

bahis siteleri sikis footballxx.3mhOPvodm2hy

porn mobileidn.LsDyWZ1plTRn

bahis porno bingoxx.y6I9QjVBxonK

bahis siteleri sikis 250tldenemebonusuxx.6Ay9ogI2Yhem

sektor benim zaten amin evladi eyeconartxx.iQbhKmEjZygJ

bahis siteleri porn sex incest vvsetohimalxxvc.QU1QiL10lNEd

porno izle tthighereduhryyy.OPEbBAVHMRj

deneme bonusu veren siteler

http://www.porn hd com gghkyogg.6bfCaQVizZw

4k sex video download ggjennifegg.514cMS7Gw5f

pornky. com ggjinnysflogg.7kusPwkEcPe

porn hd videos free download ggjgodherogg.Df9SBACVE52

Hi it me Maybell

I do not know whether it’s just me or if everybody else experiencing problems with your site.

It appears as if some of the written text within your content are

running off the screen. Can somebody else please provide feedback and let me know if this is happening

to them as well? This may be a problem with my browser

because I’ve had this happen previously. Thank you

My web page; vpn special coupon code 2024

What’s Going down i am new to this, I stumbled upon this I have discovered It absolutely useful and it has helped me out loads.

I am hoping to contribute & assist different users

like its helped me. Great job.

Visit my web-site; vpn special coupon

fashionflag full hd porn .com fashionflag.a14ZZIOSpWT

goodhere Vintage porn vurucutewet.GtL90T4l1nR

ladyandtherose BDSM porn backlinkseox.jO7tg3xgm2D

jenniferroy アラブポルノ japanesexxporns.UDItCuWSeFh

landuse Arab porn lancdcuse.mzXEoTyeoM9

Otomatik deneme bonusu veren siteler

Otomatik deneme bonusu veren siteler

falbobrospizzamadison Threesome porn jkkıjxxx.zGYQyjm1Uop

I don’t think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

MILF अश्लील qqyyooppxx.zqe8OQZj7Wt

नानी के पोर्न के बा hjkvbasdfzxzz.BFO92Ujb7ku

Heya i am for the first time here. I found this board

and I find It really useful & it helped me out a lot.

I hope to give something back and help others like you aided

me.

Here is my website – vpn special

ਡੀਪੀ ਪੋਰਨ madisonivysex.IFgmiDVg05U

ladesbet ਅਸੀਂ ਅਸ਼ਲੀਲ ਹਾਂ ladesinemi.XFOQjTI0shD

ladesbet 輪姦ポルノ ladestinemi.E84jWW5oEeg

Yes! Finally something about vpn special coupon code 2024.

sohbet karim duyguyu gotten sikin

seni bilmem de anan sektorun kralicesi 😀

sitenizi takip ediyorum makaleler Faydalı bilgiler için teşekkürler

I appreciate you sharing this blog post. Thanks Again. Cool.

bu konuda bu kadar net bilgiler internette malesef yok bu yüzden çok iyi ve başarılı olmuş teşekkürler.

Çok yararlı bir makale olmuş. Severek takip ediyorum. Teşekkür ederim.

kurdish porn

Very well presented. Every quote was awesome and thanks for sharing the content. Keep sharing and keep motivating others.

I don’t think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

child porn

Your article helped me a lot, is there any more related content? Thanks!

child porn

Excellent beat ! I would like facebook vs eharmony to find love online apprentice while you amend your web site, how can i

subscribe for a blog site? The account aided me a applicable deal.

I have been tiny bit familiar of this your

broadcast provided vivid clear concept