To have review for spyglass cdc, first we need code, here i attached 2 codes 1] cdc_test2.v is top 2] clk_rst_unit1.v is for clk and clk div and reset logic. For test there is tb.v as well

module clk_rst_unit1

( clkin,rstin,clk_div2_o,clk_div4_o,clk_div8_o,rst_o);

input clkin,rstin;

output reg clk_div2_o,clk_div4_o,clk_div8_o,rst_o;

reg q0,q1;

always @(posedge clkin,negedge rstin)

if (~rstin)

clk_div2_o <= 1'b0;

else

clk_div2_o <= ~clk_div2_o;

always @(posedge clk_div2_o,negedge rst_o)

if (~rst_o) begin

clk_div4_o <= 1'b0;

end

else

begin

clk_div4_o <= ~ clk_div4_o;

end

always @(posedge clk_div4_o,negedge rst_o)

if (~rst_o) begin

clk_div8_o <= 1'b0;

end

else

begin

clk_div8_o <= ~ clk_div8_o;

end

always @ (posedge clkin or negedge rstin)

if (!rstin) begin

q0 <= 0;

q1 <= 0;

rst_o <= 0;

end

else begin

q0 <= 1'b1;

q1 <= q0;

rst_o <= q1;

end

endmodule

module cdc_test2(din1,do1,din2,do2,clkin,rstin,clk2o,clk4o,clk8o,rsto);

input [7:0] din1,din2;

input clkin,rstin;

output reg [7:0] do1,do2;

output clk2o,clk4o,clk8o;

output rsto ;

reg [7:0] t1,t2;

clk_rst_unit1 inst(

.clkin(clkin),

.rstin(rstin),

.clk_div2_o(clk2o),

.clk_div4_o(clk4o),

.clk_div8_o(clk8o),

.rst_o(rsto));

always @(posedge clk2o ,negedge rsto)

if (~rsto)

t1 <= 8'h00;

else

t1 <= din1;

always @(posedge clk4o ,negedge rsto)

if (~rsto)

do1 <= 8'h00;

else

do1 <= t1;

always @(posedge clk4o ,negedge rsto)

if (~rsto)

t2 <= 8'h00;

else

t2 <= din2;

always @(posedge clk2o ,negedge rsto)

if (~rsto)

do2 <= 8'h00;

else

do2 <= t2;

endmodule

module clk_rst_unit1

( clkin,rstin,clk_div2_o,clk_div4_o,clk_div8_o,rst_o);

input clkin,rstin;

output reg clk_div2_o,clk_div4_o,clk_div8_o,rst_o;

reg q0,q1;

always @(posedge clkin,negedge rstin)

if (~rstin)

clk_div2_o <= 1'b0;

else

clk_div2_o <= ~clk_div2_o;

always @(posedge clk_div2_o,negedge rst_o)

if (~rst_o) begin

clk_div4_o <= 1'b0;

end

else

begin

clk_div4_o <= ~ clk_div4_o;

end

always @(posedge clk_div4_o,negedge rst_o)

if (~rst_o) begin

clk_div8_o <= 1'b0;

end

else

begin

clk_div8_o <= ~ clk_div8_o;

end

always @ (posedge clkin or negedge rstin)

if (!rstin) begin

q0 <= 0;

q1 <= 0;

rst_o <= 0;

end

else begin

q0 <= 1'b1;

q1 <= q0;

rst_o <= q1;

end

endmodule

`timescale 1ns / 1ps

module tb();

reg clkin, rstin;

reg [7:0] din1,din2;

wire clk2o,clk4o,clk8o,rsto;

wire [7:0] do1,do2;

cdc_test2 inst (

.din1(din1),

.do1(do1),

.din2(din2),

.do2(do2),

.clkin(clkin),

.rstin(rstin),

.clk2o(clk2o),

.clk4o(clk4o),

.clk8o(clk8o),

.rsto(rsto));

initial

begin

clkin = 1'b0;

forever

#50 clkin = ~clkin;

end

initial

begin

rstin = 1'b0;

#100;

rstin = 1'b1;

#5000;

end

initial

repeat (10)

begin

#200;

din1 = $random;

end

initial

repeat (10)

begin

#400;

din2 = $random;

end

endmodule

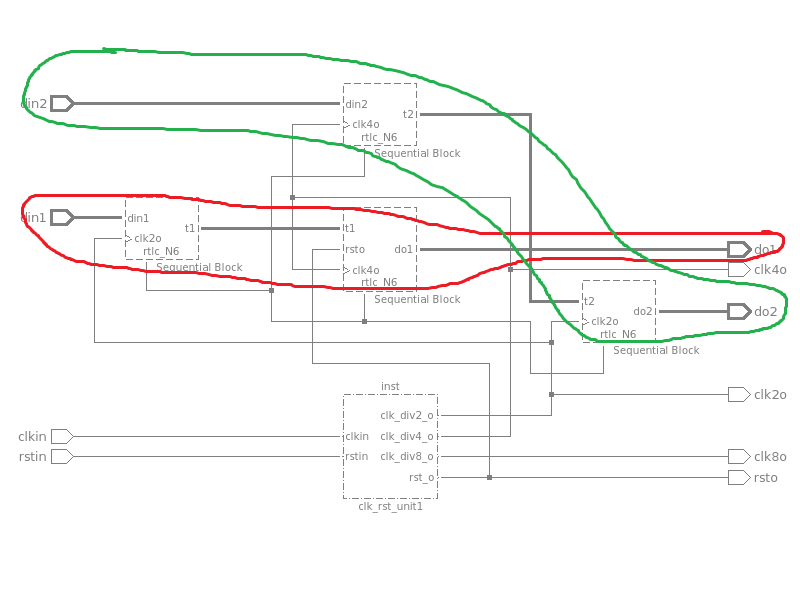

The block / schematic diagram is as below , fast to slow , slow to fast pair are there, din1 - do1 is fast to slow , din2 - do2 is slow to fast data paths

For spyglass setup, we need three files for this test setup. 1] cdc_test2.prj 2] cdc_test2.sgdc 3] verilogfilelist.f following is listing of all these three 1] cdc_test2.prj #!SPYGLASS_PROJECT_FIL #!VERSION 3.0 ##Data Import Section read_file -type sourcelist verilogfilelist.f ##Common Options Section set_option projectwdir . set_option language_mode verilog set_option top cdc_test2 set_option active_methodology $SPYGLASS_HOME/GuideWare/latest/block/initial_rtl/cdc set_option designread_enable_synthesis yes set_option report_incr_messages yes ##Goal Setup Section current_methodology $SPYGLASS_HOME/GuideWare/latest/block/initial_rtl/cdc current_goal clock_reset_integrity -top cdc_test2 read_file -type sgdc cdc_test2.sgdc set_parameter enable_debug_data yes current_methodology $SPYGLASS_HOME/GuideWare/latest/block/initial_rtl/cdc current_goal cdc_verify -top cdc_test2 read_file -type sgdc cdc_test2.sgdc set_parameter enable_debug_data yes current_goal cdc_verify_express -top cdc_test2 read_file -type sgdc cdc_test2.sgdc set_parameter enable_debug_data yes current_goal cdc_setup -top cdc_test2 set_goal_option report_incr_messages noE 2] cdc_test2.sgdc current_design cdc_test clock -name clkin -domain clkin clock -name clk2o -domain clk2o clock -name clk4o -domain clk4o clock -name clk8o -domain clk8o reset -name rstin -value 0 input -name din1 -clock clk2o input -name din2 -clock clk4o output -name do1 -clock clk4o output -name do2 -clock clk2o2 3] verilogfilelist.f ./codes/clk_rst_unit1. ./codes/cdc_test2.vv

Keep these 3 files in one folder, and in same folder make another folder of codes in which all code files present if not alter the verilog file list accordingly.

Now open the tool by command spyglass -gui , and then open project file file > open project > select the cdc_test2.prj file it automatically read the all necessary files. if it has any error it will show in cmd prompt, after this you have to click for goal option tick for required goals, there are lots of goals we can select by using option select methodology button. But for simple review we are using initial rtl hand off / cdc.

for goal there are two options block / soc , and each has different methodology accordingly its flow. by selecting any item from it, you will find the complete lists of goals as below, from that you can select according to requirement

After select the desired goal, you can run it by goal run button click, After run you get the details report for each of the goal that we select, in sub folder with project name.

you can go thro the all these goals reports or follows the msgs from msg tree, which is easy to navigate in either code or in schematic as well.

as from msg it is clear that there are 3 clocks and 2 reset are present in the design.

I will add the pre and post synthesis simulation results to check the data loss in fast to slow clock domain, either by ncsim or by dve tool along with synthesis by DC or RC-compiler.

for now please wait. for more details [of each goal] you need to ref the user manual which is more than 1000pgs.

all codes and project files will make available on request with no charge.

Comment and any suggestion are welcome, if you want any other topic/ similar blog let me know.